Core rope trong Apollo dùng chính nguyên lý “lõi lật → dây sense thấy xung”, nhưng thay đổi cách khai thác táo bạo hơn nhiều. Thay vì dùng lõi nhỏ, ít dây và chỉ lưu một bit, core rope dùng những lõi lớn hơn nhiều, cho phép rất nhiều dây sense khác nhau đi xuyên qua hoặc đi vòng ngoài quanh mỗi lõi. Lưu ý là lõi vẫn chỉ có một trạng thái từ hóa tại một thời điểm, và khi được chọn, nó chỉ lật một lần cho tất cả. Sự khác nhau giữa các bit không nằm ở “trạng thái lõi cho từng dây”, mà nằm ở đường đi của từng dây sense. Khi một lõi được chọn lật trạng thái, tất cả dây sense đi xuyên qua lõi đó cùng lúc nhận xung; những dây không đi xuyên qua thì không thấy gì. Như vậy, với một lõi, thay vì chỉ quyết định được 1 bit, ta có thể quyết định trạng thái của rất nhiều bit cùng lúc. Và vì mỗi dây sense đại diện cho một vị trí bit riêng, tức các địa chỉ khác nhau trong không gian word/strand: sợi nào chui qua lõi thì bit tương ứng sẽ là 1 khi lõi đó được đọc, sợi nào né lõi thì bit tương ứng sẽ là 0. Nói ngắn gọn, lõi từ cho ta “sự kiện lật” chung, còn việc dây nào đi qua, dây nào đi vòng chính là cách mà kỹ sư dệt nên chuỗi 0 và 1 trong core rope.

Từ core RAM sang core rope ROM

Như vậy, Core rope thực ra chỉ là một bước “bẻ lái” rất sáng tạo từ bộ nhớ lõi từ thông thường sang một dạng ROM mật độ cực cao. Ở core RAM cổ điển, mỗi lõi được coi như một ô nhớ đơn vị: một lõi gắn với một dây sense, mỗi lần kích lõi lật trạng thái ta chỉ đọc được đúng một bit, ma trận được tổ chức theo kiểu X–Y như đã nói ở phần trước. Mô hình này đơn giản, dễ điều khiển, nhưng mật độ thấp: muốn thêm bit thì phải thêm lõi.

Và với ý tưởng của core rope, một lõi sẽ có hàng chục dây đi qua

Core rope vẫn dùng lõi từ và nguyên lý “lõi lật → dây sense nhận xung”, nhưng thay vì 1 lõi = 1 bit, nó đẩy ý tưởng lên thành 1 lõi = rất nhiều bit. Người ta dùng những lõi lớn hơn, cho phép hàng trăm sợi dây đi xuyên qua hoặc đi vòng ngoài quanh mỗi lõi. Trong đó có một nhóm dây đóng vai trò sense: mỗi dây sense tương ứng với một vị trí bit nào đó trong một word nào đó. Khi ta chọn một lõi để đọc, lõi đó lật trạng thái; mọi dây sense đi xuyên qua nó cùng lúc nhận xung và được hiểu là bit 1, còn những dây sense không chui qua lõi thì không thấy xung, được hiểu là bit 0. Nhờ vậy, chỉ với một lần kích một lõi, ta có thể “thiết lập” giá trị cho rất nhiều bit cùng lúc, chỉ khác nhau ở việc từng sợi dây được dệt đi qua hay né lõi đó.

Core Rope thực tế trong sứ mạng Apollo

Trong Apollo Guidance Computer, cấu hình này được cụ thể hóa rất rõ: mỗi word, nôm na là đơn vị dữ liệu cố định độ dài của máy tính, kiểu như “một ô nhớ chuẩn” của AGC, dài 15 bit dữ liệu cộng thêm 1 bit parity, tổng cộng 16 bit. Mỗi module core rope có 512 lõi, và quanh mỗi lõi có 192 dây sense gắn logic với nó, được chia thành 12 bó, gọi là “strand”, mỗi strand gồm 16 dây. Mỗi strand tương ứng với một word: khi ta chọn một lõi và chọn thêm một strand, 16 dây trong bó đó sẽ trả lại 16 bit của word đang lưu tại lõi đó. Như vậy, mỗi lõi lưu được 12 word khác nhau, không còn là “1 lõi = 1 bit” nữa mà là “1 lõi = 12 word”. Toàn bộ hệ thống có 6 module core rope, nên tổng dung lượng ROM là 6 × 512 lõi × 192 bit, chia cho 16 bit mỗi word, ra 36.864 word, con số thường được nhắc đến khi nói về bộ nhớ cố định của AGC.

Khác biệt lớn giữa core RAM và core rope không chỉ nằm ở mật độ, mà còn ở tính chất: core RAM là đọc/ghi, có thể đổi trạng thái lõi để ghi bit mới; còn core rope là read-only theo đúng nghĩa đen, vì 0 hay 1 được quyết định bằng việc dây có luồn qua lõi hay không. Muốn “sửa dữ liệu” nghĩa là phải tháo cả module và dệt lại đường đi của dây. Chính độ “cứng” này khiến core rope cực kỳ ổn định, chống nhiễu tốt và rất phù hợp để chứa firmware bay không được phép sai sót của sứ mệnh Apollo.

Dệt phần mềm thành phần cứng

Trong thế giới core rope, khái niệm “compile” không dừng lại ở file nhị phân; bước tiếp theo là dệt phần mềm thành phần cứng. Mọi câu lệnh, hằng số, bảng dữ liệu của chương trình AGC sau khi biên dịch đều phải được chuyển thành những quyết định rất vật lý: sợi dây sense này có chui qua lõi số mấy, ở module nào, hay sẽ lách ra ngoài. Chính vì phải “lập trình bằng dây” như vậy nên quá trình sản xuất core rope vừa cực kỳ công phu, vừa đòi hỏi tổ chức và kỷ luật rất cao.

Mỗi module core rope của Apollo mất khoảng tám tuần để hoàn thiện và có giá vào khoảng 15.000 USD thời 1960s, nên phần mềm cho một chuyến bay phải được đóng băng từ rất sớm; mọi thay đổi muộn đều có giá cực đắt, vì gần như đồng nghĩa với việc phải làm lại module. Thay vì chỉ là một ràng buộc kỹ thuật, NASA và MIT còn xem đây như một “công cụ quản lý”: khi code đã được đưa vào dây, không ai có thể tùy tiện chỉnh sửa nữa, buộc đội phần mềm phải kiểm tra, review và kiểm soát thay đổi rất nghiêm ngặt trước khi chấp nhận dệt.

![Đọc chậm: Core rope, bộ não đã đưa con người lên Mặt Trăng trong Apollo hoạt động ra sao? – Phần 1插图3 [IMG]](https://photo2.tinhte.vn/data/attachment-files/2026/01/8952409_weaving-core.jpg)

Một người phụ nữ đang thực hiện việc “may” các lõi dây

Việc sản xuất core rope do Raytheon đảm nhiệm tại Waltham, Massachusetts. Họ tuyển nhiều phụ nữ có tay nghề từ ngành dệt may và chế tác đồng hồ, vì công việc yêu cầu độ khéo tay và chính xác cực cao: dùng kim rỗng luồn dây cực mảnh qua những lõi từ li ti, lặp đi lặp lại hàng trăm nghìn lần mà vẫn phải đúng tuyệt đối. Ban đầu, rất nhiều đoạn dây – như dây set, reset, inhibit – được luồn theo những pattern gần như cố định giữa các module, tạo thành “khung cứng” chung cho nhiều chương trình. Hai người công nhân ngồi đối diện, chuyền qua lại một chiếc kim rỗng chứa sẵn đoạn dây, luồn qua những lõi được chỉ định để hình thành các đường mạch cơ bản.

Khi đến phần dữ liệu chương trình, quy trình trở nên “lập trình” đúng nghĩa. Mã nguồn AGC được biên dịch bằng assembler YUL thành mã máy và xuất ra băng đục lỗ Mylar. Một hệ thống bán tự động đọc băng này và điều khiển cơ cấu cơ khí để đưa đúng lõi đến vị trí thao tác: mỗi “bước” trên băng tương ứng với việc chọn một lõi cụ thể và một dây sense cụ thể. Người thợ chỉ cần theo hướng dẫn của máy: chọc dây sense qua lỗ dẫn vào lõi nếu bit cần lưu là 1, hoặc để dây chạy lệch, vòng qua ngoài lõi nếu bit là 0. Từng bit trong chương trình, từ hằng số quỹ đạo đến đoạn mã hạ cánh, vì vậy được hiện thực hóa thành một loạt quyết định rất cụ thể: chui qua hay né lõi.

Để có được một module như vậy là cả một quá trình tỉ mỉ và đòi hỏi sự cẩn thận cực kì cao

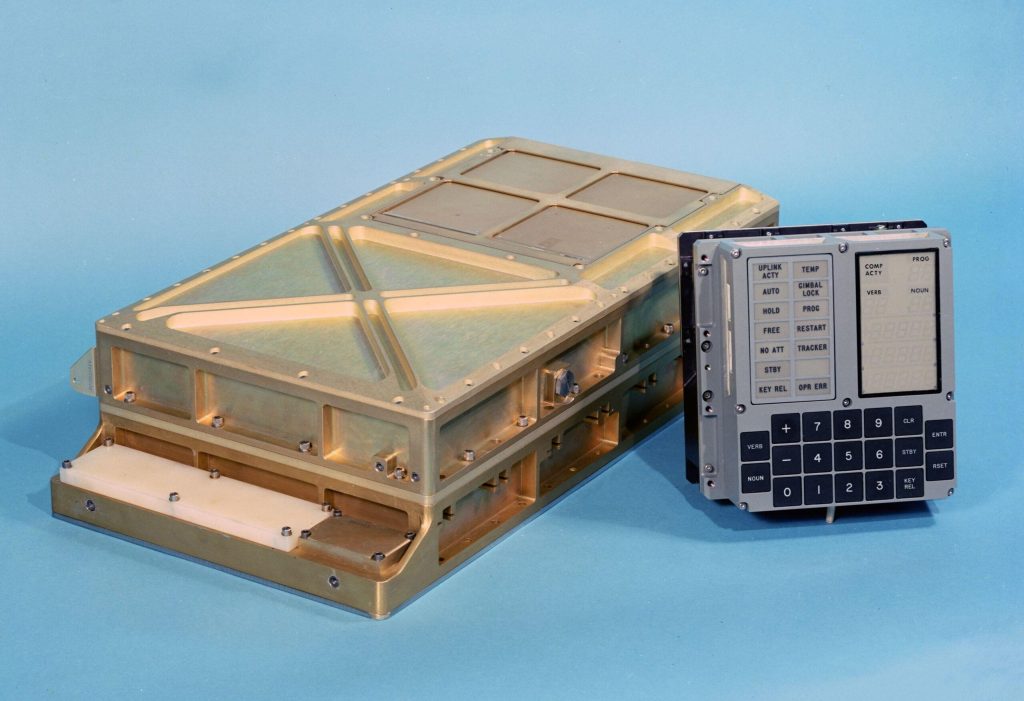

Một module core rope hoàn chỉnh, chứa phần mềm Retread 50 cho AGC

Sau khi tất cả dây sense đã được luồn xong, những chốt nylon tạm thời giữ dây trên jig được tháo bỏ, module được đổ epoxy để cố định và bảo vệ khỏi rung động trong môi trường bay. Cuối cùng, module phải qua một loạt bài test tự động: một hệ thống kiểm tra được điều khiển cũng bằng băng đục lỗ sẽ lần lượt đọc mọi địa chỉ, so sánh dữ liệu trả về từ core rope với bản chuẩn, nhằm đảm bảo không có sai sót nào trong quá trình dệt. Về sau, những module như cặp rope chứa chương trình Retread 50 được bảo tồn tại bảo tàng đã cho phép các nhóm phục chế đọc lại dữ liệu từ chính các sợi dây này, đưa chương trình quay trở lại dạng số và thậm chí chạy lại trên AGC thật lẫn mô phỏng – một vòng đời hoàn chỉnh từ phần mềm → dây → phần mềm.

AGC và phần trống ở bên trái là nơi các module core rope được lắp đặt

AGC với các module được gắn vào các khay, sau đó được kết nối với nhau qua các connectors

Một chu kỳ đọc từ core rope diễn ra thế nào?

Để hình dung cách đơn giản nhất core rope hoạt động, dễ nhất là xem nó như một quy trình gồm vài bước rõ ràng: máy cần một word, mạch giải mã xem phải “gọi” lõi nào, chọn bó dây nào, rồi đọc xung trên các dây sense và đưa 16 bit đó cho CPU. Về bản chất, mỗi lần đọc chỉ là: chọn đúng lõi, chọn đúng strand, lắng nghe xem dây nào có xung và trả về kết quả.

Từ địa chỉ lệnh đến lõi và strand

Khi phi hành gia chọn một Program trên DSKY, ví dụ như phóng, hạ cánh, v.v., AGC sẽ đặt program counter (PC) của CPU tới một địa chỉ ROM đã được quy ước là điểm bắt đầu của chương trình đó. Từ thời điểm này, mỗi lần CPU cần lấy lệnh kế tiếp, nó dùng giá trị PC ở thời điểm đó làm địa chỉ: 12 bit địa chỉ trong PC, cộng với trạng thái các thanh ghi bank, được đưa vào khối giải mã địa chỉ. Sau khi lệnh được lấy ra và thực thi, PC lại được cập nhật, thường là tăng lên một, hoặc được ghi giá trị mới nếu lệnh là nhảy, nên ở lần đọc kế tiếp, 12 bit trong PC đã là một địa chỉ khác.

Giao diện người dùng DSKY trên Apollo

Khối giải mã chỉ nhìn vào “12 bit + bank” này và quyết định rất cụ thể phải đụng vào phần cứng nào: truy cập RAM hay core rope ROM, nếu là ROM thì chọn module core rope nào trong sáu module, thuộc mặt phẳng (plane) nào, tương ứng với lõi số bao nhiêu trong plane, và trong lõi đó là strand số mấy (tức word thứ mấy trong 12 word mà lõi đang lưu). Nói ngắn gọn, PC cung cấp địa chỉ logic mà lập trình viên thấy trong mã; phần cứng bên dưới dịch địa chỉ logic đó thành một tọa độ vật lý chi tiết kiểu như: “hãy đọc module 3, plane B, lõi số 200, strand số 7”.

Mạch giải mã địa chỉ

Sau khi lệnh đã được đọc ra, bản thân lệnh này có thể chứa thêm một trường địa chỉ 12 bit để đi truy cập các ô nhớ khác (ví dụ đọc dữ liệu, nhảy tới đoạn code khác). Lúc đó, quy trình cũng tương tự: CPU lấy 12 bit địa chỉ trong lệnh, kết hợp với bank, đưa vào khối giải mã, và khối này lại chọn đúng RAM hay module core rope, lõi, strand tương ứng để đọc thêm word cần thiết.

Chọn đúng lõi: trò chơi cộng–trừ giữa set và inhibit

Bên trong mỗi module, các lõi được chia thành nhiều mặt phẳng, mỗi mặt phẳng có một dây set và một dây reset chạy xuyên qua tất cả lõi. Nếu chỉ đơn giản bơm một xung dòng trên dây set, mọi lõi trong mặt phẳng đó đều “có xu hướng” lật trạng thái. Để chỉ một lõi cụ thể lật, hệ thống dùng thêm nhiều dây inhibit, cũng chạy qua các lõi, nhưng mang dòng theo hướng ngược chiều set để triệt bớt từ trường. Mỗi lõi nằm trên một “tổ hợp” dây inhibit riêng, giống như có “vân tay” của riêng nó.

Mô phỏng đơn giản về cách core rope vận hành, với dây sense – set/reset và dây inhibit

Khi địa chỉ đã được giải mã, mạch điều khiển sẽ quyết định dây inhibit nào được cấp dòng, dây nào để hở. Với lõi cần đọc, mọi dây inhibit đi qua nó đều được giữ im, không mang dòng ngược, vì thế nó nhận trọn xung set và đủ điều kiện lật trạng thái. Với mọi lõi khác, ít nhất sẽ có một dây inhibit mang dòng ngược đi qua, dòng này cộng với từ trường ngược chiều sẽ triệt mất hiệu quả của xung set, khiến lõi đó không lật. Kết quả là, trên cả mặt phẳng với hàng trăm lõi, chỉ duy nhất một lõi thực sự đổi trạng thái từ hóa trong lần đọc này.

Chọn đúng word: bật đúng strand trong 12 strand

Khi lõi đã được chọn lật, tất cả dây sense đi xuyên qua lõi đó đều nhận một xung điện áp nhỏ; dây nào không xuyên qua lõi thì không thấy gì. Tuy nhiên, quanh mỗi lõi có tới 192 dây sense được chia thành 12 nhóm, mỗi nhóm 16 dây – đó là 12 strand, tương ứng với 12 word mà lõi đang lưu. AGC không đọc cả 12 word cùng lúc, mà chỉ cần đúng một word theo địa chỉ được CPU tìm tới. Vì vậy, song song với việc chọn lõi bằng set/inhibit, mạch giải mã địa chỉ cũng sinh ra tín hiệu “chọn strand” – xác định nhóm 16 dây nào sẽ được nối về mạch khuếch đại.

Mạch chọn strand

Bên trong module rope, các dây sense đi vào một mạng điện trở và diode tương đối phức tạp. Mạch chọn strand ở bên ngoài sẽ nâng đường chọn tương ứng lên một mức điện áp đủ cao, phân cực các diode sao cho chỉ dòng của đúng nhóm 16 dây (strand được chọn) mới có đường “thoát” về biến áp sense và mạch khuếch đại; những strand còn lại bị diode chặn lại, coi như bị cô lập. Như vậy, mặc dù có 192 dây sense đang nằm trong module, tại thời điểm đọc chỉ có 16 dây thuộc strand được chọn là thực sự “nói chuyện” với phần còn lại của hệ thống.

Biến xung nhỏ thành 16 bit cho CPU

Ở bước cuối cùng, mọi thứ quay lại đúng nguyên lý đã nói: dây sense nào đi xuyên qua lõi vừa lật sẽ nhận một xung; dây sense nào đi vòng ngoài thì không. Trên 16 dây của strand được chọn, vị trí nào có xung tương ứng với bit 1, vị trí nào im lặng tương ứng với bit 0. Tuy nhiên, xung trên dây sense rất nhỏ và dễ bị nhiễu “bẩn” từ các xung set/reset mạnh xung quanh, nên trước khi về tới CPU, tín hiệu phải đi qua biến áp và các IC sense amplifier chuyên dụng. Những mạch này làm việc theo kiểu vi sai: chúng so sánh hai đầu tín hiệu, loại bỏ phần nhiễu chung và chỉ “nhạy” với sự lệch nhỏ do xung từ lõi tạo ra, rồi khuếch đại và chuẩn hóa thành mức logic rõ ràng.

AGC có các module khuếch đại sense riêng cho RAM lõi từ và cho core rope, nhưng đầu ra của chúng được nối chung lên bus dữ liệu 16 bit của CPU. Vì thế, ở góc nhìn của phần mềm, đọc một word từ ROM trong core rope hay từ RAM lõi từ gần như giống nhau: CPU đưa địa chỉ, đợi một chu kỳ, rồi nhận lại một word 16 bit. Sự khác biệt lớn nằm hoàn toàn ở phía sau hậu trường: với RAM, bit 0/1 được quyết định bằng trạng thái từ hóa của từng lõi; với core rope, 0/1 được quyết định ngay từ khi sản xuất, bằng việc dây sense đó có đi xuyên qua lõi hay không.

Nguồn: [1][2][3][4]

công nghệ, khoa học, kĩ thuật, mẹo vặt, cộng đồng, thảo luận, hỏi đáp, sửa lỗi, máy tính, sự cố, camera, lỗi điện thoại, lỗi máy tính#Đọc #chậm #Core #rope #bộ #não #đã #đưa #con #người #lên #Mặt #Trăng #trong #Apollo #hoạt #động #sao #Phần1769967331